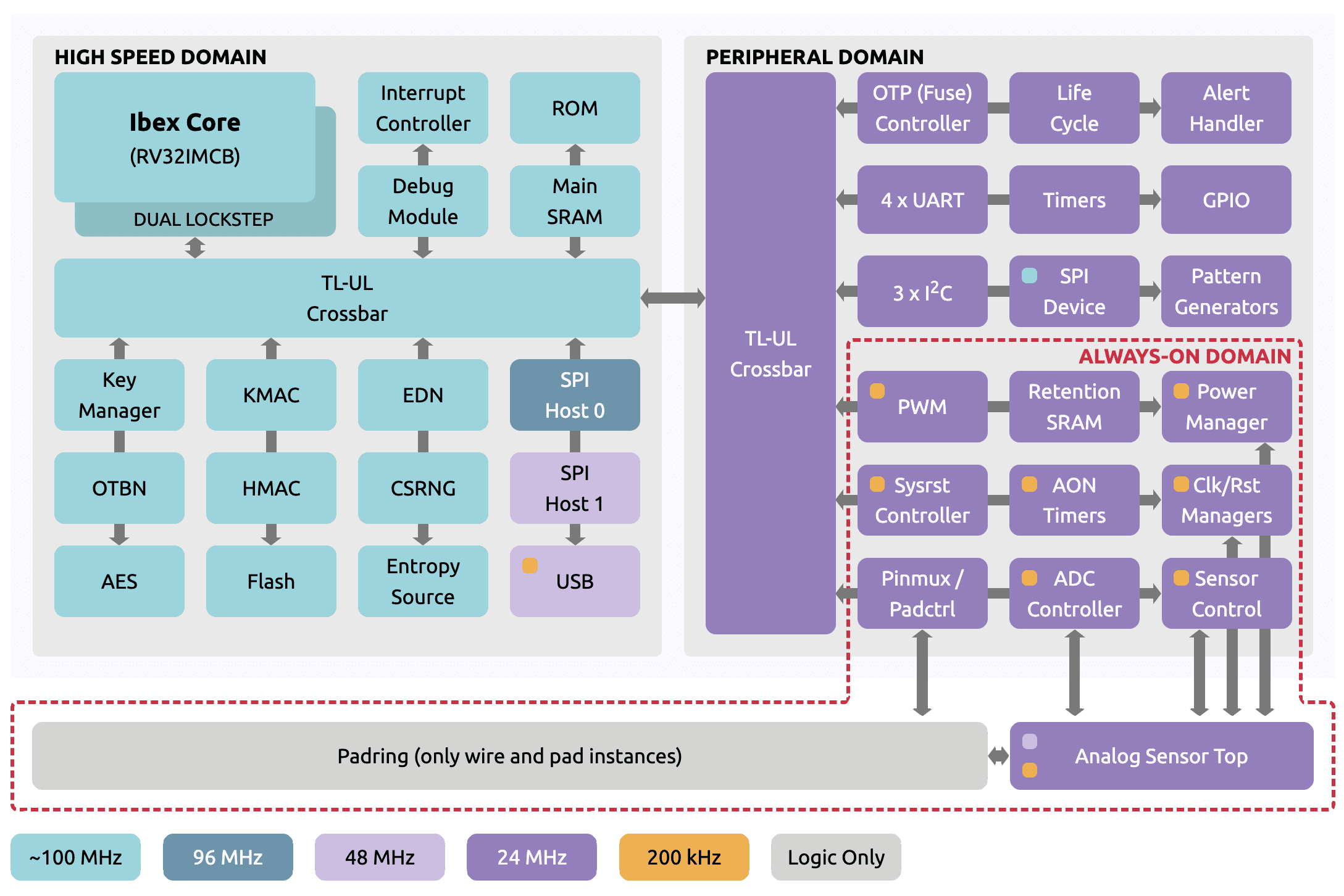

OpenTitan®, the world’s first open-source silicon root of trust, offers commercial-grade security in a transparent, verified and flexible design.

- World’s most active open-source silicon project

- Secure by design – not obscurity

- Designed for certification: FIPS, NIST and CC

- Hardened against SCA and FI

- Standalone SoC or integrated as a Secure Enclave

- In production for Google Chromebooks and datacentres

- Roadmap for full post-quantum cryptography

- Permissively Licensed (Apache 2.0)

Ibex® is a production-quality open-source 32-bit RISC-V CPU core written in SystemVerilog

- Low power consumption

- Small area footprint

- Predictable performance

- Dual-core locked step

- Security Hardening

Engineering consultancy

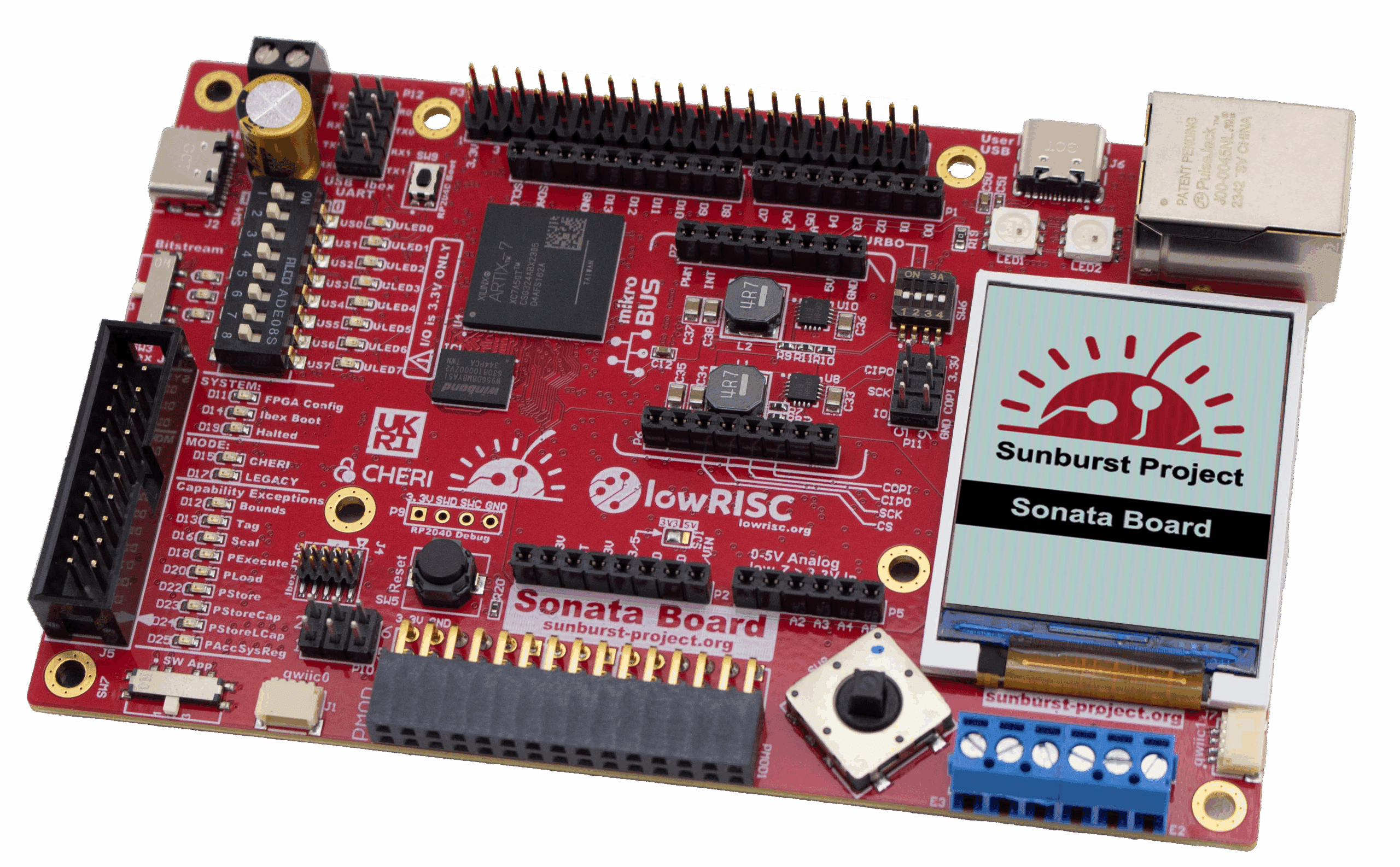

lowRISC® has a full stack engineering capability, with deep expertise in:

- Processors and compute subsystems

- Memory safety and CHERI

- Hardware and formal verification

- Security

We do top-quality engineering consultancy work around our open-source projects and third-party ones, as proven by our contributions to CHERIoT-Ibex, COSMIC and Caliptra.

lowRISC news

About us

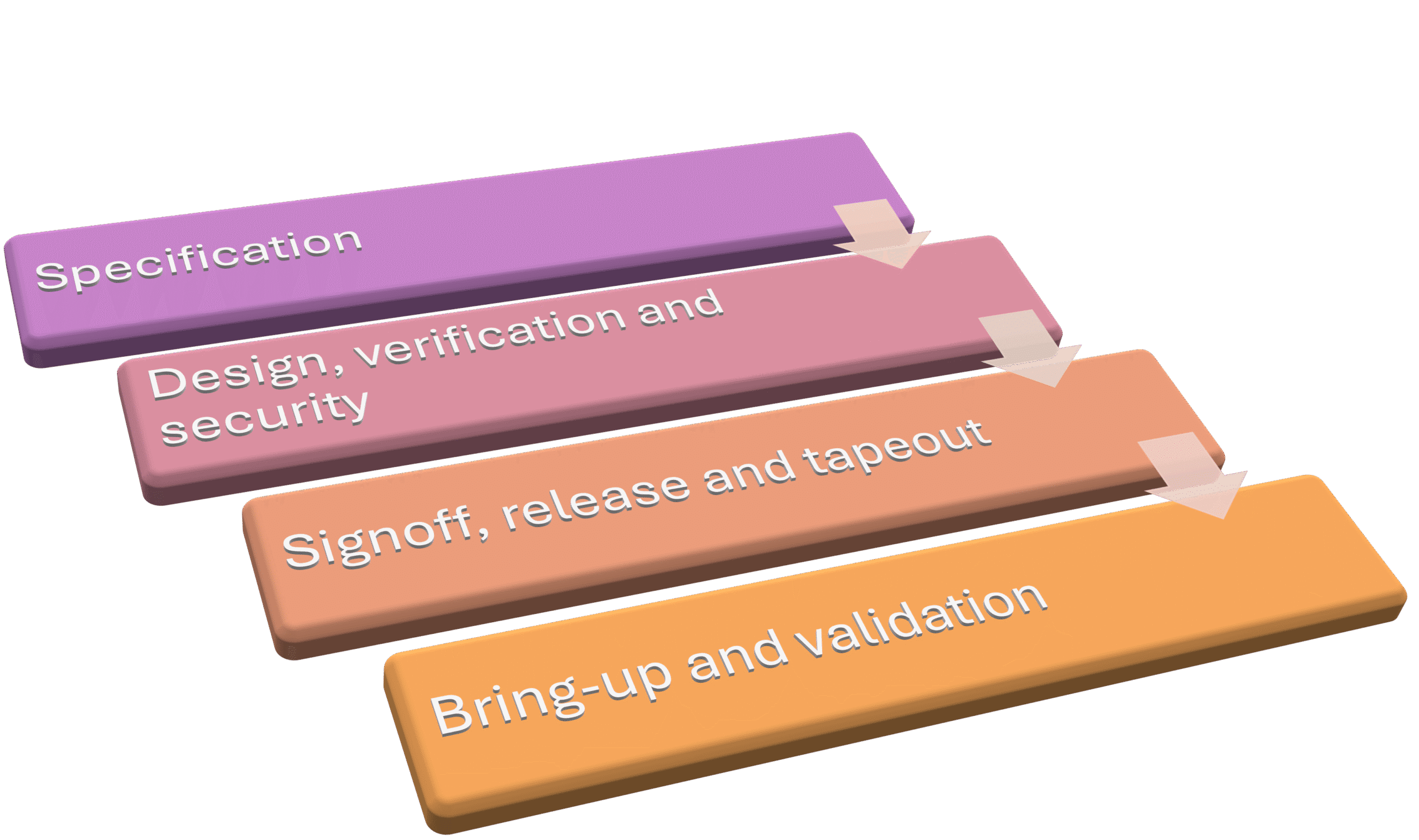

lowRISC is a not-for-profit company that uses collaborative engineering to develop and maintain open-source silicon designs, software and tools, through a unique combination of skills, expertise and vision.

We provide a home for multi-partner projects that deliver high quality, thoroughly verified IP, which provide a solid foundation for the rapid development cycles required by new silicon products.

lowRISC employs engineering teams in Cambridge (UK) and Zurich (Switzerland), working on our own developments and partner projects aligned with our mission.

Contact